## Soutenance de thèse de Loan PHAM-NGUYEN

Lundi 16 Novembre 2009 - 14h30 – à l'amphithéâtre M001 Phelma Polygone (anciennement bâtiment ENSERG) – Minatec Nord

## THEORETICAL AND EXPERIMENTAL STUDY OF ADVANCED FULLY-DEPLETED SOI MOSFETS

In the last forty years, technological advances have been achieved mainly by reducing the size of transistors in order to improve the circuit density manufacturing cost and operating frequency. However, the current trend of miniaturization causes undesired effects degrading the electrical parameters and transistor performance. In order to counteract these effects, many technological solutions have been proposed to optimize the existing architectures or to introduce novel structures. Among these solutions, silicon-on-insulator (SOI) is considered as a technology that can overcome some of the major issues of bulk silicon technology. SOI technology offers advanced transistor architecture in particular fully-depleted MOSFETs which are the object of our study. This thesis is dedicated to theoretical and experimental studies of advanced fully-depleted MOSFETs on SOI substrate. We carried out different characterization techniques to investigate the impacts of emerging boosters on the major electrical parameters as well as on the performance of FD structures. We concentrate on the study of three technology solutions: (i) high-K materials, (ii) tensile/compressive CESL, (iii) TiN/TaN metal-gate. Besides, we also used electrical measurements combining with an analytical model to discriminate the dominant effects responsible for the degradation of one of the key parameters: carrier mobility.

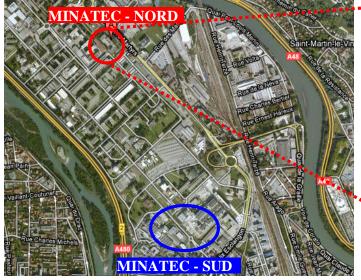

> Amphithéâtre M001 - MINATEC NORD 23 rue des Martyrs Grenoble

Partir de la gare par le **bus 34** ou de Minatec Sud (terminus tram B) par le **bus 30**

Arrêt: Ecole d'Electronique